次のステップで回路設計を行います。

1.シンボルの作成

2.回路の設計(描画)

3.ファイルの保存

4.VHDLファイルへの変換

登録したQsysを使って、シンボルとVHDLファイルを作成します。つぎ回路図エディタを使って入出力を追加し回路化します。描いた回路を次に、ファイルを添付しますので参考にしてください。(ダウンロードしてQualtusで開きます。)

次のステップで回路設計を行います。

1.シンボルの作成

2.回路の設計(描画)

3.ファイルの保存

4.VHDLファイルへの変換

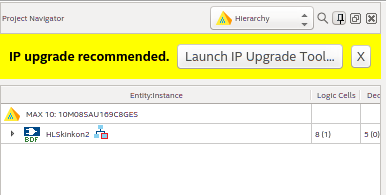

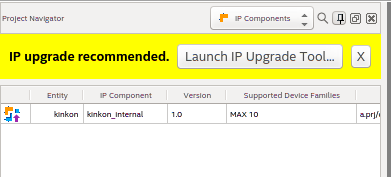

1.右上のProject Navigateorを[Hierarchy]から[IP Components]に変更します。

⇒

⇒

2.Prooject Navigateorの窓に、kinkonというQsysが出てきますので、ダブルクリックします。(Qsysの登録忘れでQsysが出てこなかった場合は、[Project]-[Add/Remove File in Project]で登録ができます。)

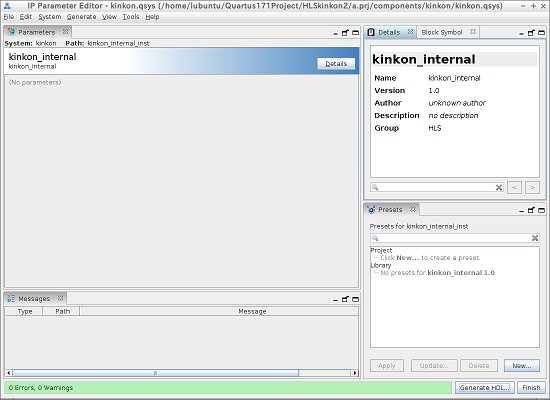

3.Prooject Navigateorの窓に、kinkonというQsysが出てきますので、ダブルクリックします。時間がかかりますが、次のような画面が出てきます。

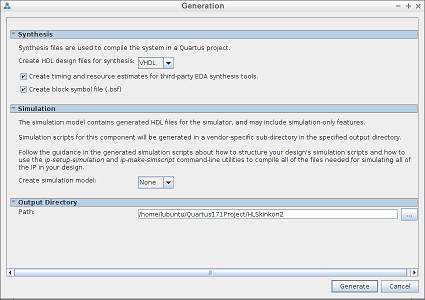

4.右下の[Generate HDL..]を押し、画面を次のように設定します。

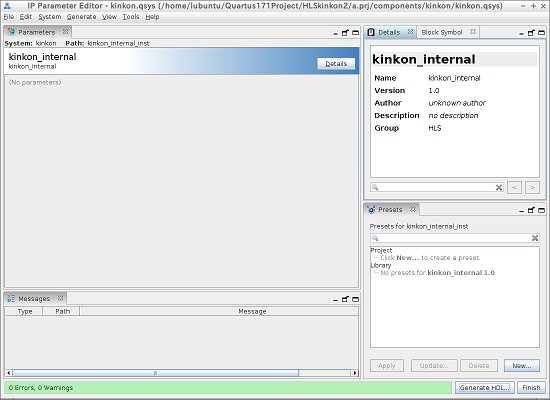

5.右下の[Generate]を押し、VHDLファイルとシンボルファイルを作成します。変換が終了すると元の画面に戻るので[Finish]を押します。

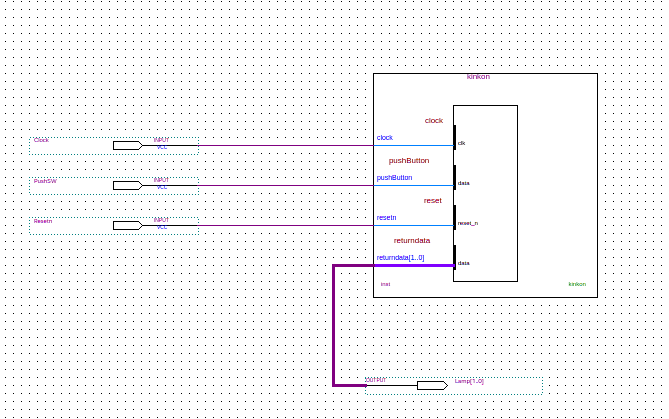

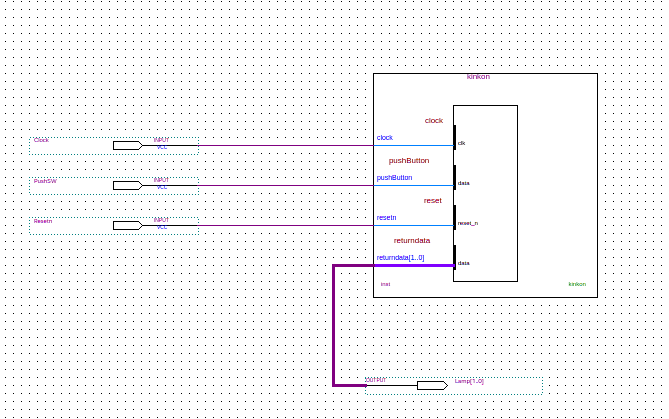

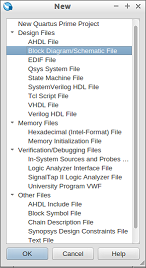

1.[File]-[New]をクリックします。次の画面で「Block Diagram/Schematic File」を選択してエディタを起動します。

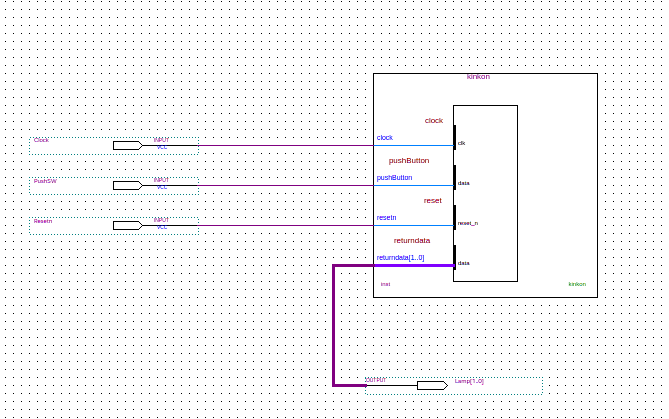

2. のボタンを押して部品を選択します。今回使用した部品を次の表に記します。選択したら[OK]を押しエディタに配置します。選択の解除はキーボードで[Esc]を押します。

のボタンを押して部品を選択します。今回使用した部品を次の表に記します。選択したら[OK]を押しエディタに配置します。選択の解除はキーボードで[Esc]を押します。

| 機能 | 記号 | 階層 | 記号名 |

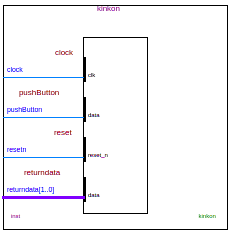

| kinkonシンボル |  | [Project] | kinkon |

| 入力ピン |  | [Primitive]-[pin] | input |

| 出力ピン |  | [Primitive]-[pin] | output |

を押して部品間を接続します。Output側は、バスですので太い線で結び、端子名の一番後ろに[1..0]をつけてください。

を押して部品間を接続します。Output側は、バスですので太い線で結び、端子名の一番後ろに[1..0]をつけてください。

[File]-[Save As]でファイルに名前を付けて保存します。

回路図をFPGAのプログラムにしたりシミュレーションをするのに利用するためVDHLに変換します。変換後のVDHLファイルはこれです。もし、回路設計が面倒だという人はこれを利用してください。

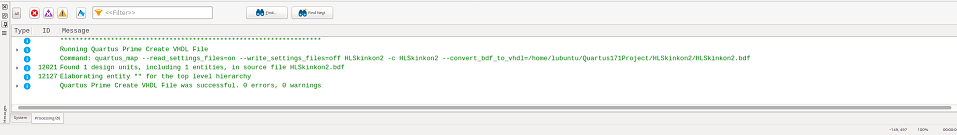

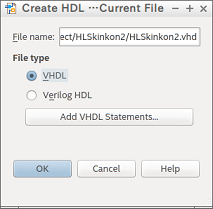

1.[FIle]-[Create/Update]-[Create HDL Design File from Current File...]をクリックします。

2.次の画面でFile TypeにVHDLを選択して、File nameを念のため確認し[OK]

3.Messages窓に次のように「Quartus Prime Create VHDL File was successful. 0 errors, 0 warnings」が出てきたら成功です。

赤文字やerrorsに数字があがっているようでしたら回路がどこかで間違っています。変なところが接続点になっていないかなどよく見直ししてください。